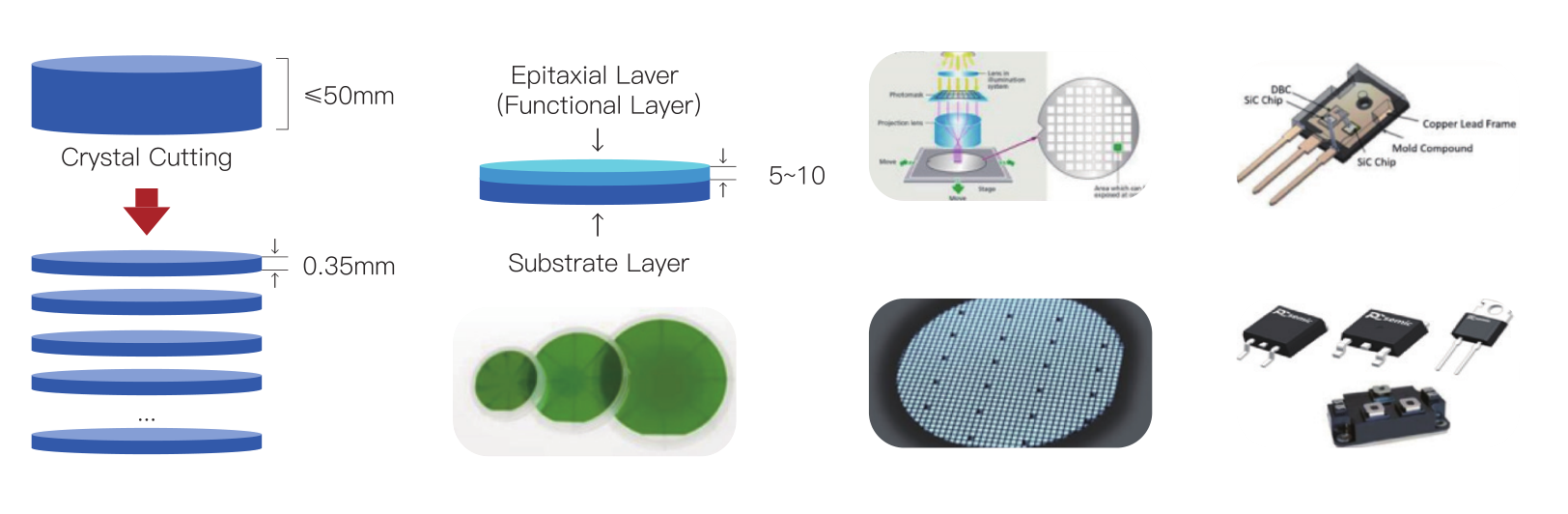

SiC Power Device Fabrication Process Flow

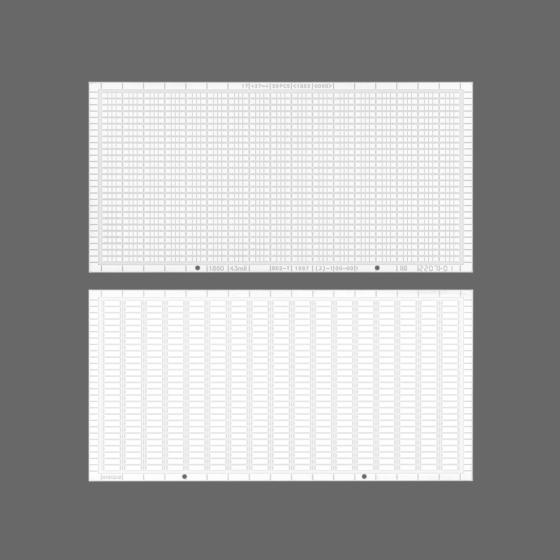

1. Substrate Preparation

1. Substrate Preparation

Core Objective: Obtain high-purity, low-defect SiC single-crystal substrates.

Crystal Growth: SiC powder is sublimated and deposited on a seed crystal via the Physical Vapor Transport (PVT) method at >2000°C, forming a SiC ingot.

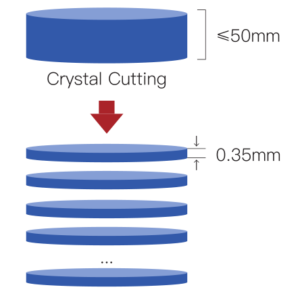

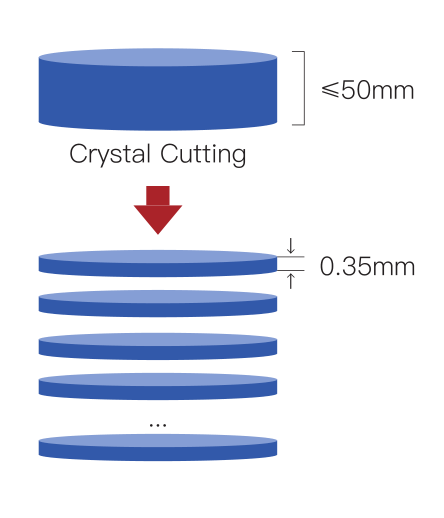

Wafer Processing:

Cutting: Diamond wire saws slice the ingot into wafers (thickness ≤1mm) with edge crack reduction using laser-assisted techniques34.

Polishing: Chemical Mechanical Polishing (CMP) achieves surface roughness <0.5nm.

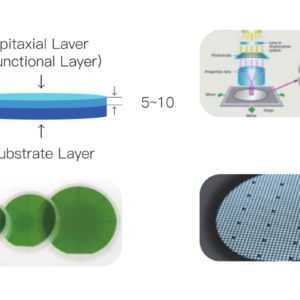

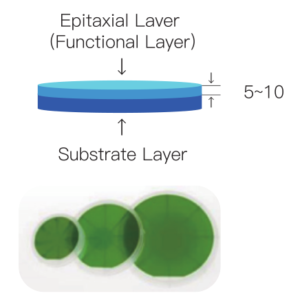

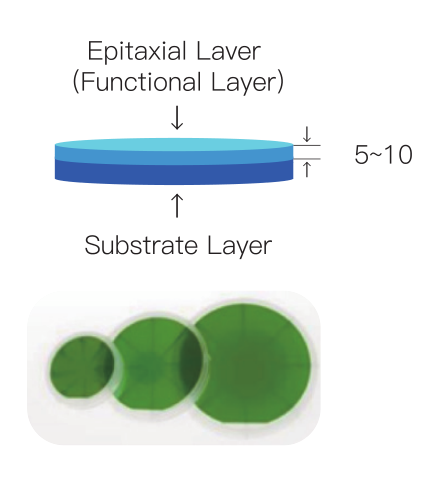

2. Epitaxial Growth

Core Objective: Deposit high-quality SiC epitaxial layers (e.g., N-type drift layers).

Chemical Vapor Deposition (CVD):

Reactants: SiH₄ and C₃H₈ at 1500–1700°C, with in-situ doping (N or Al) for uniform carrier concentration.

Defect Control: Photoluminescence (PL) or X-ray diffraction (XRD) detects dislocation density (<1×10³ cm⁻²).

3. Device Fabrication

Core Objective: Form functional structures (e.g., MOSFET gates, PN junctions).

Oxide Layer Formation:

Dry thermal oxidation (1200–1300°C) or Atomic Layer Deposition (ALD) creates SiO₂/Al₂O₃ gate dielectric layers (interface traps <1×10¹¹ cm⁻²·eV⁻¹).

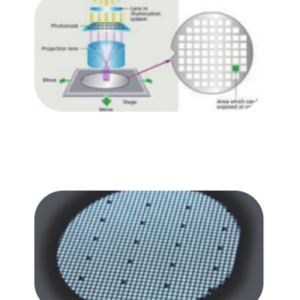

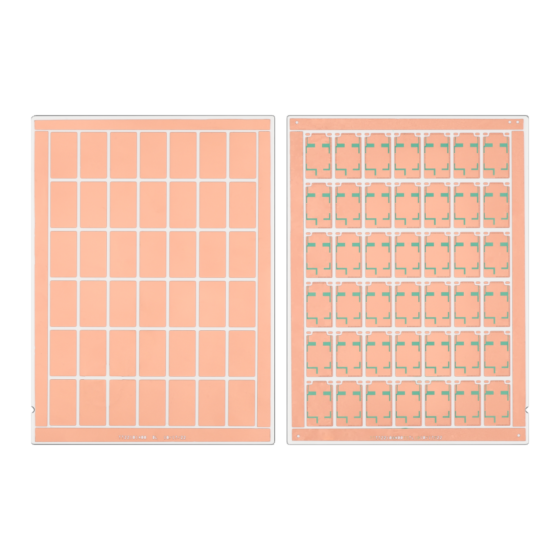

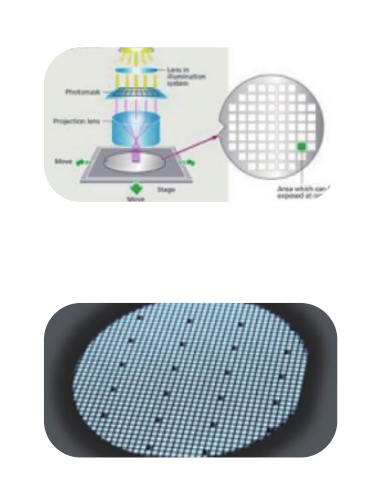

Lithography & Ion Implantation:

Photolithography: UV exposure defines patterns with linewidth ≤0.5μm, adapted for SiC’s hardness using specialized equipment.

Ion Implantation: Al (P-type) or N (N-type) ions are implanted and activated via high-temperature annealing (>1600°C).

Metallization & Etching:

Electrode Deposition: E-beam evaporation of Ti/Al/Ni layers (200–500nm) for source, drain, and gate contacts.

Mesa Etching: Reactive Ion Etching (RIE) isolates devices with etch depths of 3–5μm.

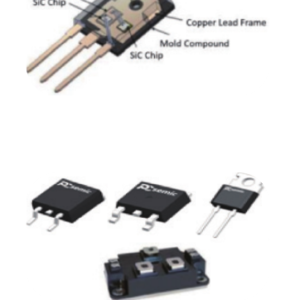

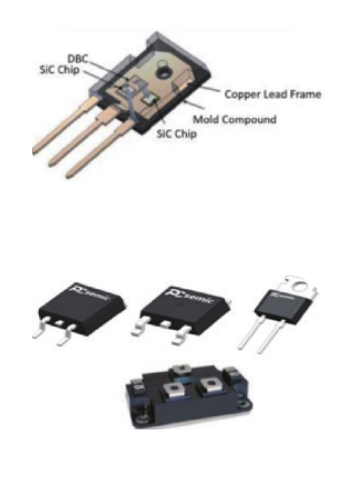

4. Packaging & Testing

Core Objective: Ensure reliability and performance under high-voltage/high-temperature conditions.

Die Attach:

Silver sintering bonds chips to substrates at 250°C and 20MPa (shear strength >30MPa).

Module Assembly:

Wire Bonding: Au or Al wires connect electrodes.

Encapsulation: High-temperature-resistant materials (e.g., silicone gel) protect against thermal stress.

Electrical Testing:

Static Parameters: Breakdown voltage (Vbr ≥1700V), on-resistance (Rds(on) <50mΩ).

Dynamic Parameters: Double-pulse testing evaluates switching losses (Eoss <10μJ).

Key Process Innovations

Substrate Defect Mitigation: Laser-assisted cutting reduces edge chipping.

Epitaxial Uniformity: In-situ doping optimizes carrier concentration gradients.

Advanced Packaging: Nano-silver paste replaces solder for 250°C operation.

This process integrates the latest advancements from industry and academia, tailored for high-voltage EV and renewable energy applications.

GIM

GIM