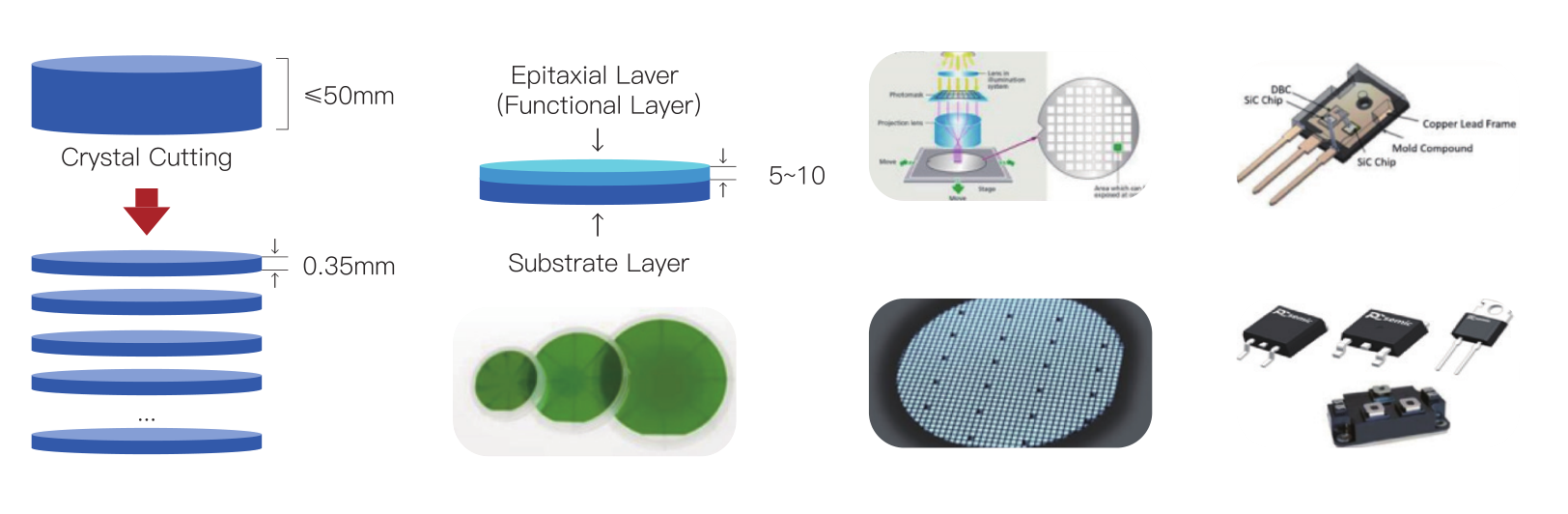

Fluxo do processo de fabricação de dispositivos de energia SiC

1. Preparação do substrato

1. Preparação do substrato

Objetivo principal: Obtenha alta pureza, substratos de cristal único de SiC com baixo defeito.

Crescimento de Cristal: O pó de SiC é sublimado e depositado em um cristal de semente através do Transporte Físico de Vapor (PVT) método em >2000°C, formando um lingote de SiC.

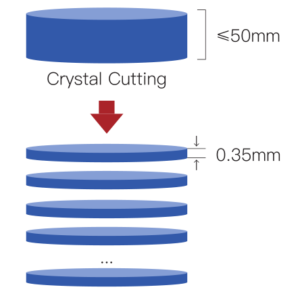

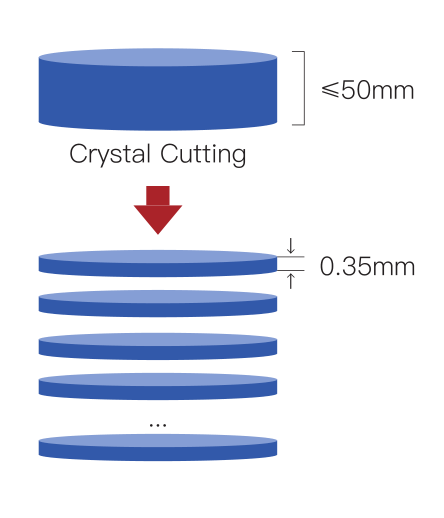

Processamento de wafer:

Corte: As serras de fio diamantado cortam o lingote em bolachas (espessura ≤1mm) com redução de trincas nas bordas usando técnicas assistidas por laser 34.

Polimento: Polimento Químico-Mecânico (CMP) atinge a rugosidade da superfície <0.5Nm.

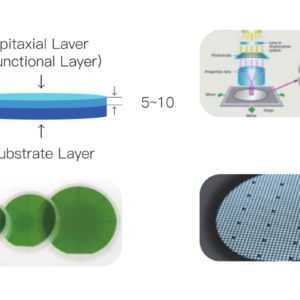

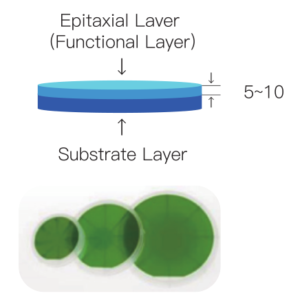

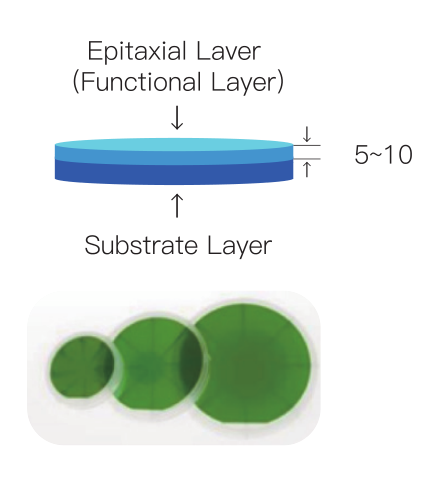

2. Crescimento Epitaxial

Objetivo principal: Depositar camadas epitaxiais de SiC de alta qualidade (por exemplo,, Camadas de deriva do tipo N).

Deposição de vapor químico (DCV):

Reagentes: SiH₄ e C₃H₈ a 1500–1700°C, com dopagem in-situ (N ou Al) para concentração uniforme do transportador.

Controle de defeitos: Fotoluminescência (PL) ou difração de raios X (XRD) detecta a densidade de deslocamento (<1×10³ cm⁻²).

3. Fabricação de dispositivos

Objetivo principal: Formar estruturas funcionais (por exemplo,, Portas MOSFET, Junções PN).

Formação de Camada de Óxido:

Oxidação térmica seca (1200-1300 ° C) ou Deposição de Camada Atômica (ALD) cria camadas dielétricas de porta SiO₂/Al₂O₃ (armadilhas de interface <1×10¹¹ cm⁻²·eV⁻¹).

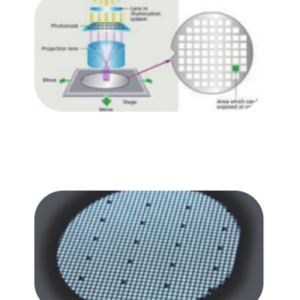

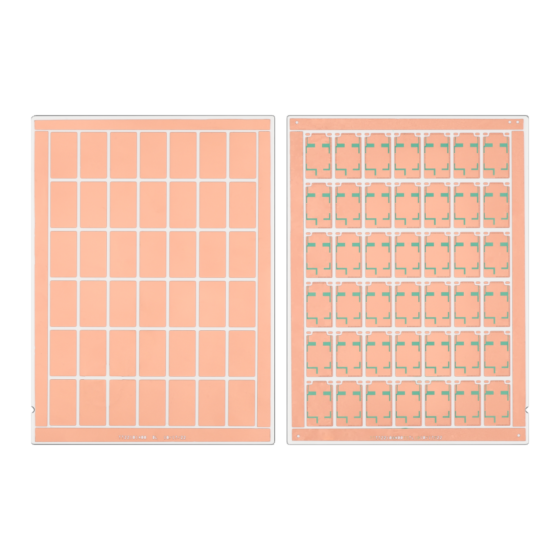

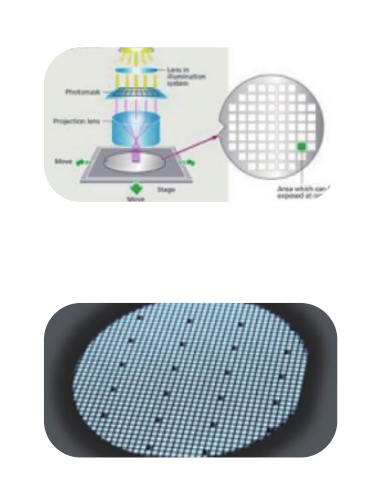

Litografia & Implantação de íons:

Fotolitografia: A exposição UV define padrões com largura de linha de ≤0,5 μm, adaptado para a dureza do SiC usando equipamentos especializados.

Implantação de íons: Al (Tipo P) ou N (Tipo N) Os íons são implantados e ativados por meio de recozimento de alta temperatura (>1600°C).

Metalização & Gravura:

Deposição de eletrodos: Evaporação por feixe E de camadas de Ti/Al/Ni (200–500 milhas náuticas) para a fonte, drenar, e contatos de portão.

Gravura de mesa: Gravação de íons reativos (RIE) isola dispositivos com profundidades de gravação de 3 a 5 μm.

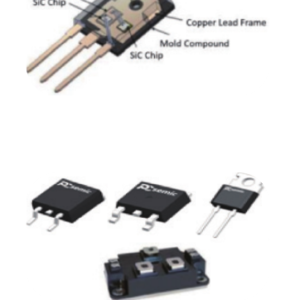

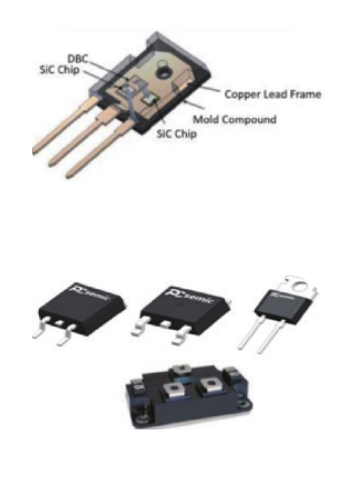

4. Empacotamento & Teste

Objetivo principal: Garanta confiabilidade e desempenho em condições de alta tensão/alta temperatura.

Anexar Matriz:

A sinterização de prata une os cavacos a substratos a 250 ° C e 20 MPa (resistência ao cisalhamento >30Mpa).

Montagem do módulo:

Ligação de fios: Fios Au ou Al conectam eletrodos.

Encapsulação: Materiais resistentes a altas temperaturas (por exemplo,, gel de silicone) proteger contra o estresse térmico.

Testes elétricos:

Parâmetros estáticos: Tensão de ruptura (VBR ≥1700V), na resistência (Rds(em) <50mΩ).

Parâmetros dinâmicos: O teste de pulso duplo avalia as perdas de comutação (Eoss <10μJ).

Principais inovações de processo

Mitigação de defeitos de substrato: O corte assistido por laser reduz o lascamento da aresta.

Uniformidade Epitaxial: A dopagem in-situ otimiza os gradientes de concentração do portador.

Empacotamento avançado: A pasta de nano-prata substitui a solda para operação a 250 ° C.

Este processo integra os mais recentes avanços da indústria e da academia, sob medida para aplicações de EV de alta tensão e energia renovável.

MENSAGENS

MENSAGENS